Alchip’s 3DIC Validation Paves Way for 2nm–3nm Stacked Architectures

Proven dual-die integration and ecosystem readiness mark a major step toward scalable 3DIC designs driving next-generation AI and high-performance computing innovation.

Alchip Technologies, the dedicated high-performance and AI computing ASIC leader, validated its 3DIC ecosystem readiness with results from its 3DIC test chip tape out.

The results vaulted Alchip into a clear 3DIC technology leadership because it validated an entire, integrated 3DIC solution, as well as its various elements. The test chip provided CPU/NPU core demonstration, UCIe and PCIe PHY preparation, Lite-IO infrastructure, and third-party IP. The latter is particularly important because any 3DIC proven IP is hard to find.

Alchip’s 3DIC test chip success holds greater than normal implications because it provided technical validation of the company’s 3DIC ecosystem. Alchip’s growing ASIC ecosystem assures AI and HPC developers of a fast time-to-design, accurate pathway for highly complex ASIC devices. Alchip’s industry-leading ecosystem encompasses a technology-specific design flow, package design flow, die-to-die IP, and interconnect.

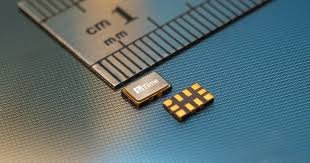

Tape out validation is a critical step because 3DIC elements differ significantly from their 2D counterparts. Alchip’s device integrates a 3nm top die and a 5nm base die, assembled using TSMC’s SoIC®-X packaging technology. It is designed to stress test power density and thermal dissipation challenges inherent in 3D integration. The results also inform future 3DIC designs incorporating 2nm and 3nm stacked chiplets.

The chip includes a CPU, NPU core and high-power logic on the top die. The base die integrates a network-on-chip, L3 cache, and interface IP. The two dies are connected using APLink-3D Lite IO. The tape out validated several critical 3DIC capabilities, including:

- Cross-die synchronous die-to-die IP.

- Design-for-test strategies with redundancy, repair, and process monitoring.

- Signal and power integrity analysis for 3D stacking.

- Thermal and mechanical simulations for vertical integration.

- 3D physical design implementation and verification.

“The tape out proves our design flow, selected die-to-die IP, and interconnect IP,” said Erez Shaizaf, Alchip CTO. “It’s a significant milestone that confirms our readiness.”

The dual-die design required a new approach to physical and logical integration. The EDA tools and design methodologies were updated to support co-design across both dies. Sign-off included electrical, timing, and mechanical integrity across the full 3D assembly.

The company tested Interface IP, architected specifically for 3DIC. Interoperability and full functionality demanded new IP. Each die, especially the bottom die, requires custom PHY implementations for protocols such as UCIe, and PCIe.

3DI/O timing represents another major advancement. Alchip has limited die-to-die latency to 40 picoseconds, enabling timing paths that span dies without degrading performance. A fully integrated 3D clocking structure ensured coherent operation across both layers with minimal timing skew.

Four IP vendors participated in the test chip program. Two contributed proven hard macros. Two others evaluated new IP on the test platform. An EDA flow vendor collaborated to ensure tool and methodology readiness.